#### How do you create a logic gate using just 24 silicon atoms?

#### Join ASML as an Electronics Engineer and help push the boundaries of technology.

As one of the world's leading providers of lithography systems for the semiconductor industry, we bring together the most creative minds in science and technology to help produce increasingly cheaper, faster and more energy-efficient microchips.

For the past 25 years, we've been helping to realize Moore's law. Now we want to go even further: to enable the tripling, or even the quadrupling of chip-feature density every two years. That's why we need talented Electronics Engineers. People who can, for example, increase the speed and the precision of our systems integration, and thereby enable future logic gates no bigger than a few silicon atoms. It's just one of the many electronics challenges at ASML. And there are countless more – all targeted at achieving more than Moore's prediction.

If you're up for these challenges, we'll put you in a multidisciplinary team and give you plenty of freedom to experiment and learn new skills. What Moore could you want?

For students who think ahead

# Halfway

At the time of writing, we're about halfway through this college year. The new quartile has begun and most of you will probably be enjoying your new courses (or trying to pass some again). When you're reading this, you'll probably know whether you passed them or not. As a board, it is about we showed some of the things we've accomplished and tell you about other things we failed to do. We've been busy for half a year, and we've had enough time to get some things done.

One of the new things we've set up is called Satis. Most of the work on this project is done by our (beloved) webteam. Satis is a web environment that should help most committees with their administration. Every committee has meetings, makes minutes of these and some members even have tasks they should do. Satis is supposed to help with this. As of now, Satis has only a few modules. A task module to keep track of the tasks of members, a module to reserve a room for meetings and a failure module to keep track of failed tasks. At the moment there is even a module which enables committees to upload their own promotional posters to the television slide show. The webteam is working on more modules, so when you're reading this, they probably have finished some more. Satis is fully in development and the webteam need all the feedback they can get. Try Satis out [1] and give them your feedback so they can make it even more awesome.

Something most committee members probably don't know anything about are the so called "commissieinstellingsbesluiten" or committee rules and regulations in my best English. This is a document that every committee has. In this the rules and regulations of the committee are described. Most of these documents are filled with what a committee should be doing with their time. Unfortunately, most of these documents are horribly outdated and as far as I know, most active members do not even know that these exist or haven't seen them in years. For example, according to their "CIB", the Borrel should organise drinks every other week in the Tombe. As far as I know, the Tombe doesn't exist anymore. Thus for now, our plan is to update these CIB's and make them more accessible to our members so everyone knows what they should be up to.

Well, I have used most of the space I get in this corner of the Vonk. Nothing more to report here, so read on and enjoy this edition of the Vonk.

Op de koningin, op Scintilla

Koen Zandberg President of E.T.S.V. Scintilla

[1] http://satis.scintilla.utwente.nl (only on intranet) Author: Koen Zandberg

#### Hardlopers zijn doodlopers Thursday April 25th, 2013 16:00h, Sportsbar Abscint

#### 41st Batavierenrace

Friday, April 26th, 2013 15:00h, Nijmegen - Enschede

#### 77th Cantus Scintillae Thursday, May 2th, 2013 20:00h, Abscint

#### Symposium

Wednesday, May 15th, 2013 9:00h, Spiegel 1

#### - table of contents -

#### Masthead

#### De Vonk

Periodical of E.T.S.V. Scintilla. Published four times a year in the amount of 630 copies.

Year 31, edition 2 Februari 2013

#### Editorial team

Tim Broenink, Erwin Bronkhorst, Arno Geurts, Tijmen Hageman, Fieke Hillerström, Maikel Huiskamp, Peter Oostewechel, Ray Tanuhardja, Rowan de Vries, Marcel Wenting.

Print

Gildeprint, Enschede

#### Editorial office

Material vonkkopij@scintilla.utwente.nl

All members of Scintilla receive De Vonk free of charge by post.

Nothing in this magazine may be duplicated or copied without explicit permission from the editorial team of De Vonk.

The editorial team reserves the right to change or exclude material provided by third parties, in part or in whole. The opinions expressed in the articles are not necessarily shared by the editorial team.

#### ISSN 0925-5421

Due to the high amount of wireless transmitters in our society, the available and free frequencies in the air become harder to find and use. However, the demand for available bandwidth is increasing with each new wireless technology that is introduced. To find and use the scarce free frequency bands, cognitive radio (or CR) can be used. In this Dutch article, you can read what research about cognitive radio is done at the UT.

17

4

22

In this Vonk, you will find a new, recurring subject: the Chain Reaction. The goal of this article is to give someone else the opportunity to react on the previous main article. In this edition, some comments on 3D electronics are given, based on the main article of the previous Vonk about 3D self-assembled electronics. Can the self-assembled electronics from the previous article be used with analog, digital and mixed signal electronics?

Presidential Note Halfway

News News for the electical engineer

Education Educational update

SolarTom Starting from scratch

Hobby Wireless for € 5,-

On location TE Connectivity

Project ACDC<sup>-1</sup>

Chain reaction 3D electronics 2B

Main article Cognitive radio

Photo pages

####

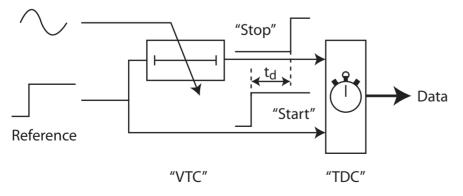

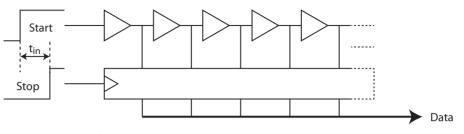

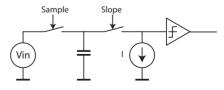

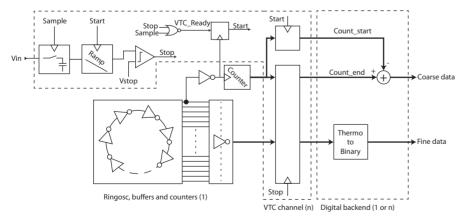

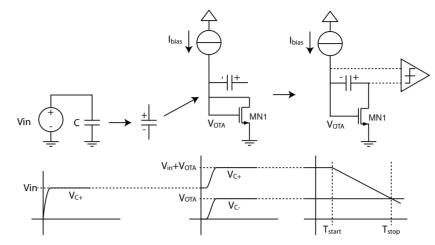

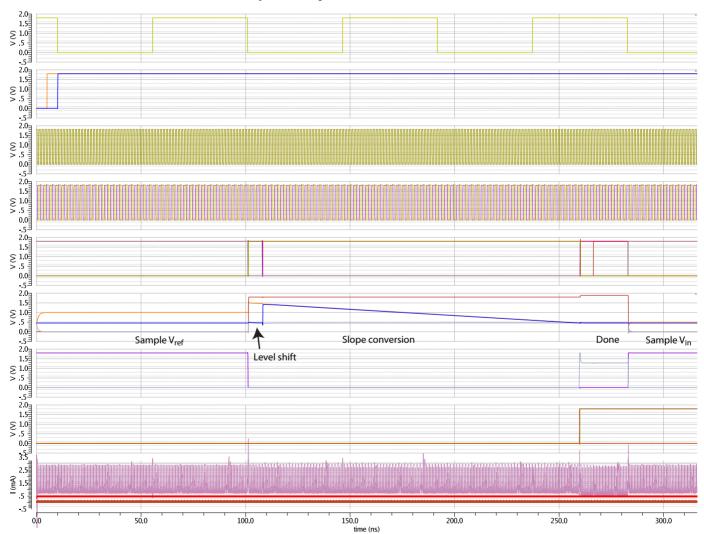

Dirk-Jan developed a new technology in analog to digital conversion, by making use of a new time-based method. The method analog to two ways of measuring the speed of a runner: you can measure the amount of time that the runner needs to run 400 meter, or you can measure how far the runner can run in one minute time. Each method has its own benefits and drawbacks. The same holds for the ADC domain and in this article, the developed technique is being discussed.

**Empowering the**

24

26

31

32

34

39

40

42

43

future

Traditionally, Scintilla organizes a symposium every year. This year, the symposium will take place in May and the subject of the symposium is "Empowering the future". In this article, the organizing committee will explain what you can expect from this day and what kind of speakers will be there to show you their view on this subject. If you still don't know if you want to attend, read the article and enrol for this event.

Scintilla Operating Team Logical Volume Manager

> Symposium EMPowering the future

> > Hobby Baking pies part 2

Master thesis Voltage-time ADC

> Vonk forge Volcanus' sparks

Junction Pepijn Assendorp

Column *hhddvvddbvd*

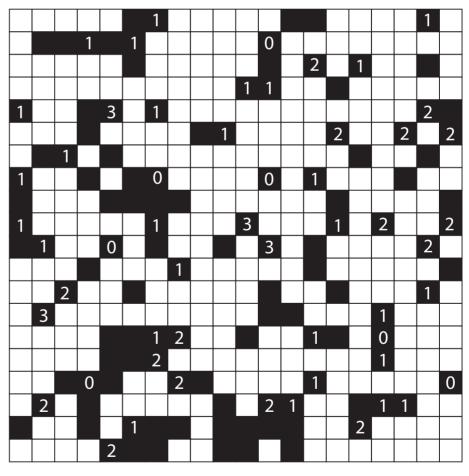

Puuzle

#### Editorial

#### Connectivity

We are always connected in some way to something. Almost all people are connected with each other via Facebook, whatsapp, twitter or some other way with their smartphones. Cities are connected with roads and railroads, and sending a message between these cities can be done in seconds via mail. We are all so depended on these connections to work, or just be there, that we do not know what to do when they are gone. For some people it is the end of the world when they have no reception on their phone. What if they miss something in those minutes their phone has no connection.

But sometimes you make new connections when the ones you trust on are gone. Take for example when the trains are stopped because of a power outage. Normally when you sit in the train you look out the window or read a book, but there is no interaction with the other people in the train. But when the trains are stopped everybody is talking with one another. Some people start complaining to each other that the trains are not running and the staff can't give you directions, some people try to find their bus to the next station while others start joking about everything they can think off. All these people are now connected in some way. Well until the bus they are waiting for arrives, than it is free for all and the new connection disappears as fast as it appeared.

Maikel Huiskamp

# News for the Electrical Engineer

Author: Tijmen Hageman

#### MIT demonstrates fastest p-type transistor

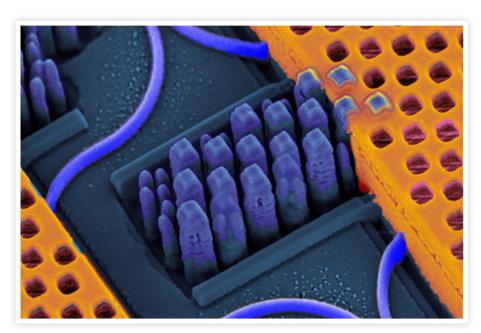

Researchers at the Massachusetts Institute of Technology have developed a record setting p-type transistor. The device is twice as fast as previous experimental p-type transistors and almost four times as fast as the best commercial p-type transistors. Rather than silicon, the tri-gate device is made of the semiconductor material germanium. The increased carrier mobility results from a special fabrication process placing the germanium atoms closer together than they would find comfortable. This `straining' process is performed by growing the germanium on top of several different layers of silicon and a silicon-germanium composite. The germanium atoms naturally try to line up with the atoms of the layers beneath them, compressing them together.

The experimental transistor, blue indicating the areas of `strain', where atoms are placed closer than normal.

#### Source: web.mit.edu

#### IBM shows breakthrough in nanophotonics

For over a decade, IBM has researched the integration of photonic components into electrical circuits, referred to as 'silicon nanophotonics'. Recently, they have announced a working prototype created with 90 nm semiconductor technology. Photonics have shown that they allow much faster communication compared to conventional electronic methods. The integration of photonic and electrical circuits in a single chip provides a cost-effective solution for highspeed data communication. The prototype of IBM integrates optical components such as wavelength division multiplexers (WDM), modulators and detectors alongside CMOS electronics, achieving over 25 Gbps per channel.

Sources: www.tweakers.net, www-03.ibm.com

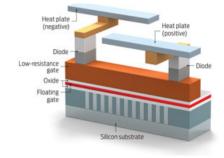

#### Self-repairing flash memory developed

The company of Macronix has developed a self-repairing flash memory unit. Although flash has many advantages, it only supports up to roughly ten thousand read/write operations. This is caused by the fact that flash cells make use of a `floating gate', a layer of material embedded within layers of insulation. By inserting or removing electrons from this layer, a bit is written. Mass read/write operations degrade the insulation, however, and the cell will eventually fail. Macronix figured that when heating the memory cells to 800 degrees centigrade for several milliseconds, the cells can be renewed. They found that the memories held well over 100 million cycles using the technology. The technique is not new: earlier a similar result was obtained by heating the entire chip to 250 degrees centigrade for several hours. This research yielded another surprise: it was found out that heating allows for faster erasing, a process that was thought to be independent of temperature.

#### Source: spectrum.ieee.org

#### Toshiba develops low-power MRAM

Toshiba has announced a new version of the prototype memory element referred to as `spin transfer torque magnetoresistive random access memory' (STT-MRAM). MRAM is a next-generation memory technology, exploiting the resistive properties of magnets in different orientations. MRAM is a promising all-round memory technology, as it combines speed, scalability and non-volatile. The prototype of Toshiba has reduced the power consumption by a factor 10, making its power consumption lower than that of SRAM. Especially the fact that MRAM is non-volatile makes it a suitable alternative, also retaining the information in powerless situations.

Source: www.techpowerup.com

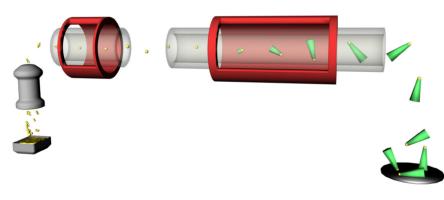

#### New production process semiconductors developed

Researchers at the Lund University of Sweden have developed a new method of creating semiconductor electronics. Instead of starting from a silicon wafer, the researchers have made it possible for the structures to grow from freely suspended nanoparticles of gold in a flowing gas. A process of self-assembly grows the semiconductor material around the gold particles. The growth can be controlled by temperature, time and the size of the gold nanoparticles. With the help of a series of prototype ovens, the researchers expect to be able to develop several types of nanowires, such as pn-diodes. Not only is the production method very fast and cheap, it also provides a continuous process instead of the traditional batch process that is currently the norm in wafer fabrication.

Bron: www.lunduniversity.lu.se

## Graphene/nanotube hybrids developed

Researchers at the Rice University have developed a very high surface density electrode. For this purpose, they first grew a graphene substrate (sheet of carbon, 1 atom thick) on metal. Then, they grew a forest of carbon nanotubes from this substrate. By growing them from the substrate, the electrical contact between the nanotubes and the metal electrode is seamless. The resulting electrode consists of a forest of nanotubes with a height of 120 microns, delivering more than two thousand square meters per gram of material. As the quality of an electrode increases with increased surface, this is a remarkable number.

Source: news.rice.edu

# Educational update

The big educational changes that have been introduced in 2012 also have their influence on the education in 2013 and beyond. I will highlight the biggest changes that were announced recently and will become active within the coming months. Still, a lot is unsure, so watch your e-mail for messages from the university or read the updates that Scintilla will provide.

#### Deadlines for Bachelor and Master assignments

#### Bachelor

Since September 2012 it is mandatory to set a deadline for your bachelors assignment. When you have the first appointment to discus your bachelor assignment with your supervisor you should set a start and end date. The performance in the assignment shall be assessed on the closing date, regardless of the stage of your work. If the grade for the assignment is below a pass grade, the chair may give the student the opportunity to continue working on the assignment so as to meet the requirements for a pass grade. The extra time allowed shall however be limited to 3 credits. The grade for the assignment may not exceed a 6 in this case. If the student's performance is still unsatisfactory after the extra time has run out, the student has to do a new assignment on another theme and with a different supervisory committee or under the authority of another chair.

#### Master

For the master theses a deadline has to be set when the planning is discussed. When

this deadline is reached the work will be reviewed and graded. If the grade does not meet the requirements for a pass grade the student gets two months extra. The grade for the assignment may not exceed a 6 in this case, if the grade is still too low a new master assignment must be chosen.

## Rescheduled resits 4th quarter

This year the resits of the 4th quarter will not be held in the last two weeks of the summer holiday. Instead these resits will take place in week 30 (22 July -26 July). The regular courses of the fourth quarter will be tested in week 26. The resits of the third quarter will take place in week 27.

#### Clustering bachelors degree programs

The faculties will disappear and instead all bachelor programs will be divided into clusters. Electrical engineering will be in the "information & Communication Technology" cluster. The clusters are made in such a way that the programs within the clusters can share modules. This does not mean that a program cannot share a module with an Author: Laurie Overbeek

other cluster. Instead of a program director for every program we will now have seven directors of education, one for every cluster. The director of education will lead a cluster of courses and mainly fulfill management tasks. They will be responsible for the quality and cohesion of courses within their clusters and pursue new teaching methods.

#### "The faculties will disappear and instead all bachelor programs will be divided into clusters."

#### Why a clustering of the educational programs?

The UT is currently working towards the redesign of all bacholar programs according to the Twente Educational Model (TEM). This model is based on modular educational projects. The University Board wants to group the educational programs in seven clusters. Educational programs with a substantial overlap should benefit from the cluster environment as it simplifies the design process and it should also encourage the educational programs to share modules.

## SolarTom

Last time I wrote that the Solarteam project is very similar to other projects. It isn't anymore. It becomes more and more clear that we do not only have to design, but actually build a solar car. From scratch. This means not only assembling every piece of the car, but also finding all of the parts. For free, if possible, and otherwise we also have to collect funding to pay for this. This means that a lot of time is spent looking for companies that are prepared to sponsor parts. Sometimes small (two heatsinks, a couple of brackets, a few connectors) and sometimes large (6 m<sup>2</sup> of solar cells, a complete battery-pack, a few motors).

Another big difference is that the standard scientific layout (describe current situation, propose improvement, test, compare) can't be used on everything that has to be designed, mostly because there is a lack of time. The word multitasking got a new meaning for me. A common day at the moment consists of calling and e-mailing multiple companies, soldering a small PCB, looking into software somebody else wrote, doing some measurements on solar cells and a Solid-Works layout, and finishing the day by preparing a meeting.

On the more technical side of the story I can't bring you a lot of news right now. It is very exciting for us to slowly see the first

parts coming in, but I can not show them to you yet. The frame of our mockup arrived last week and by the time you are reading

#### "We are looking for the best even money can't buy yet."

this it should be fully functional. A large box in the mail from Vermeulen Print Service brought us a large panel with all of our designed prints, so we could start soldering and programming.

Author: Tom Kooyman

In the meanwhile, we are busy with our search for solar- and battery cells. It might not seem to be much of a challenge to buy these components, but it is a challenge to buy state-of-the-art cells. We are not looking for the best money can buy, we are looking for the best even money can't buy yet.

The same is true for the electrical motor that will drive our solar car. In order to know what the motor is capable of, it has to be tested on a motor test bench. And again, I had to find one myself, for free if possible. There is a small company in the south of Holland, called Dynostar, that could help us out. Their company designs and build dynamometers, and they happened to have an old test bench lying around. Have you ever had a scooter? And have you ever had it tested by the police? Chances are that same ROLLERBANK is now used to test our motor.

Right now, we are at the end of the design stage for most parts, but we are not even close to having a functional car yet. After the first tests we will know how much redesigning has to be done and I will keep you up to date in the next edition of the Vonk. If you can't wait that long, there is a blog post every now and then at *www.solarteam.nl*.

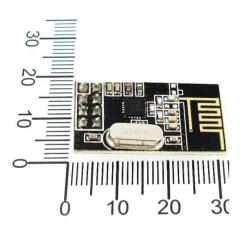

## Wireless for €5,-

Wireless communication is one of the big steps towards making great projects. For what is more awesome than a small robot driving around your room? Five of these robots communication wirelessly with one another. This brings me to this hobby project; to try to set up a wireless connection using a NRF24L01 module, which can be found at the STORES for just € 3,85.

Figure 1: The NRF24L01 Module

The first thing that can be noticed when opening the datasheet of this module is that it contains the things you would expect on a wireless module, including modulators, filters and amplifiers. One of the more unique properties of this little guy is the baseband processing engine. It contains system for the transmission, validation, acknowledgement and retransmission of 'Shockburst' packages. This means that the transmitter handles everything needed for getting your data to the other side. You only have to provide the data.

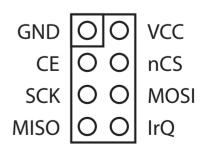

If you want to use this module there is one thing you should keep in mind. It has a maximum supply voltage of 3.6 V. This shouldn't be a problem for most microcontrollers, because they can operate at 3.6 V or 3.3 V, but it is something that can go wrong. The pinout scheme of the module can be seen in figure 2. The VCC an GND need no explanation, neither do the standard SPI pins (nCS, MOSI, MISO, and SCK). The only two marginally special pins are the CE (chip enable) and the IrQ (interrupt request). CE will make your transmitter actually send or receive data and IrQ signifies that something has happened in your chip. That was the simple part. We can now connect the module to our project. For this purpose I used an Atmega88. I connected the Power and SPI pins to their equivalent on the microcontroller and connected CE to PB1, nCS to PB0 and IrQ to PD7.

#### "Congratulations! You've just send data over the air."

We can now talk to the module. If we look in the datasheet we can find that the module expects a 8-bit command when nCS is pulled low. At the same time it will output its status register. After this it will listen for or transmit up to 5 bytes of data, depending on the given command. To test whether the module is responding we can now send the NOP (0xFF) command. This will only return the status register. The status register should be (0x0e) on a newly started transceiver.

Sending commands is one thing, but we need to do a lot more if we want to actually

Author: Tim Broenink

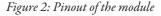

transmit data. If we look at the state diagram from the datasheet (figure 3) we can see that in order to transmit the data, we will first need to switch to standby mode. After that we can set the data to transmit and transmit. So we will first need to set the PWR\_UP bit in the configuration register. In order to neatly write this data we will first need to read this register, change the bit and then write it back to the module. Now the module will actually do something. Lets take a look at the other settings of the transceiver. The default transmit settings can be found in the table of figure 4. For now we will leave most of these settings be. One thing we will change is the RF channel, for the 2.4 Ghz band is also used for Wi-Fi. If we look at the current standards for Wi-Fi (IEEE 802.11n) we can find that the its band stops at 2.4835 GHz (see figure 5). For this purpose we will put our RF channel at 2.496 Ghz. We can set this frequency using the RF\_CH register. According to the provided datasheet the RF channel will be 2.4 + (0.001 \* RF\_CH) GHz. So we will set it to 96.

Figure 5: Wi-Fi Channels. As we can see in the diagram, the newer Wi-Fi standards use the channel up to 4.835 GHz. All standards remain below 2.5 GHz.

Figure 3: State diagram from the datasheet

In order to actually transfer data, we will have to fill the TX buffer. We can do this by sending a W\_TX\_PAYLOAD command.

We can now write data to the TX buffer. In order to check whether this data has arrived in the module we can check the TX\_EMPTY flag in the FIFO\_STATUS register. If we then pull CE high, the module will start to transmit. After some time we can read the status again. You will notice that the MAX\_RT bit was high. This is caused by the fact that we don't have a receiver to ACK the packet. So our transmitter will retransmit the package 3 times and then give up. In order to fix this we will need a receiver. The receiver has a few different settings, but not many. We will need to set the PRIM\_RX bit in the CONFIG register and we will have to set 'receive pipe 0', which has the same address as the transmitter, to a width of one byte. This is done by setting RX\_PW\_P0 to 1.

If we now send a byte using the W\_TX\_ PAYLOAD command and pulling CE high on the transmitter.

If the receiver is enabled during this transmit, CE high, PWR\_UP, then the transmitter should receive an ACK packet from the receiver and will change its status to 'Data sent' (TX\_DS). We can now recover the sent byte on the receiver side by using the R\_RX\_PAYLOAD command. This should return your sent byte. If so: congratulations! You've just send data over the air. If not, you should try to debug using the datasheet and fix it.

Now that the ether is yours to use, you can hopefully think of some awesome projects to make with this. I know that I do and you might see those future projects in another Vonk.

| Setting                   | Default Value |

|---------------------------|---------------|

| Address Width             | 5 bytes       |

| Number of Retransmissions | 3 tries       |

| RF channel                | 2.402Mhz      |

| Data Rate                 | 2Mb/s         |

| TX address                | 0xE7E7E7E7E7  |

Figure 4: Default transmitter settings

# **TE Connectivity**

As Commissioner external affairs of Scintilla I get to visit a lot of different companies at different locations. Once there I often get a short (or not so short) tour of the facilities. During these tours I can see some of the stuff a company is working on. One of my more memorable visits was my visit to TE connectivity. Author: Tim Broenink

connectivity

As far as my company visits go, this one started out quite well. TE connectivity is situated on a fairly large terrain, surrounded by other companies. I could however easily spot their building. TE connectivity is a company corking in many different sectors: Transport technology, Network technologies, Industrial and fabrication technology and consumer goods. Their facility in Den Bosch however specializes in Fiber, Connector and Cable assembly. This was also the subject of my tour. I got to see everything that was involved in the designing, testing and producing of these assemblies. The first part of my tour was to a large lab filled with large machines. The purpose of these machines remains a bit of a mystery to me, but some of it was explained. The

year 31 edition 2 purpose of most of the machines was the same, to manipulate glass fibers in such a way that they could be used. This started simple, with a laser cutter designed to precisely cut a fiber such that it could be inserted

#### "This monster of a machine was used to 'print' glass fibers"

into a connector. However it quickly got more complex. One of the most impressive machines I saw there was a large 3-d printer like structure. This monster of a machine was used to "print" glass fibers into a plastic

substrate. Resulting in a network of fibers locked in plastic. This could be integrated in circuit boards in order to provide a middle ground between on-chip waveguides and loose fibers.

After this large lab, we came to a more familiar environment, a lab like we would recognize here. In this lab I saw a lot of different, mostly electrical tests. From simple current and voltage ratings, to complete measurements of the response of a connector. The setups included maximum current tests. Which used very thick cables and a setup shielded from people with Plexiglas. As you can imagine what happens when you exceed a maximum current for these cables, you can probably understand while this shielding was necessary. But these are the tests you expect on a electrical connector, however there were a few more unexpected tests as well. It is surprising how many aspects of a cable, connetor or assembly need to be tested in order to determine its suitability.

A complete section of the lab was dedicated to durability test. I saw their environmental chambers which cycled the connectors through different temperatures and humidity levels. It went from freezing temperatures to approximately a hundred degrees Celsius. Combined with a humidity ranging from almost zero to a hundred percent, tis put a lot of stress on the connectors. I saw dust chambers which tested the connector in dry and dusty environments. It even had a little wiper on the front, which was used to clear the glass window of dust so one

could see the actual test. I even saw a gorilla test setup, where a cable was attached to a weight which was subsequently rotated around the axis of the connector to test it's mechanical robustness. This was of course also tested in other ways. One of the ways to test the durability of the product was to manually connect and disconnect the connector a lot of times. There was an automatic setup available, but it wasn't able to reproduce the exact effect from human handling. So it had to be done manually. That does sounds like a good summer job, doesn't it?

Some of the more awesome setups to watch were the radio rooms. These were too large rooms in the middle of the lab. The inside of one of the rooms looked like something you would get if you would cross a shark with a children's playpen. The whole room was covered in large foam spikes in order to dampen electromagnetic waves. This was used to test electromagnetic radiation from connectors, cables and antennas. One of the radio rooms took up a very prominent place in one of the electrical labs. There were large racks of measurement and analysis equipment around the chamber, to measure the electromagnetic radiation from the setup inside. In my opinion this chamber could also be used to play a very interesting game of marbles, or maybe a strange version of twister.

There were more tests that I could go into detail on, but I think this gives a good impression of the things I saw. The next and last part of my tour involved the workshop of the facility. This workshop is used to fabricate connectors and parts when the amounts required were less than they wanted to produce with mass production. My surprise however, was pretty big when I saw the workshop there. During my visit, one of the larger machines was busy extruding casings for connectors, when I asked how many connectors there were, I was told there would be about five thousand. When I think of manual production, I think of about three units. I guess I was wrong. There were machines in the workshop that could create metal parts, extrude casings and assemble these. I saw a few large molds for plastic casings, large sheets of metal being punched into the desired shape, and even a machine which assembled the parts of the product to complete system. I didn't even get to see the whole workshop, so I expect there to be a lot more. The next time I think of manual production, I guess I will see a large extrusion mold, punching out a few units per second, or something like that.

This marked the end of my tour. I had seen some of the internal workings of TE connectivity. However I expect that there is a lot that I haven't seen.

"When I think of manual production, I think of about three units. I guess I was wrong."

We quickly returned to the point of our meeting, where we had some time to look at the special system worked into the wall next to the door. There was a tablet like system that showed whenever the conference room was booked in an agenda. One could see how long the next meeting in the room would take and who would be there. A small thing to notice at a time like this, but is was told that they were busy with rebuilding parts of there facilities and this was one of the new innovations employed. I thought is was rather useful.

With that I had already reached the end of my tour at TE connectivity. I have seen some things that showed me how they work and operate and I hope that I have transferred some of my impressions of this interesting visit. I have learned something from it, and maybe you have too. There is of course a lot more going on at TE connectivity then the brief overview I have just given you, but I think that you will be able to find out more for yourself, if you want to.

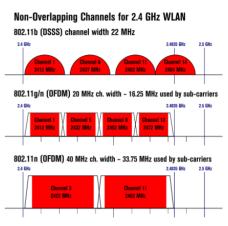

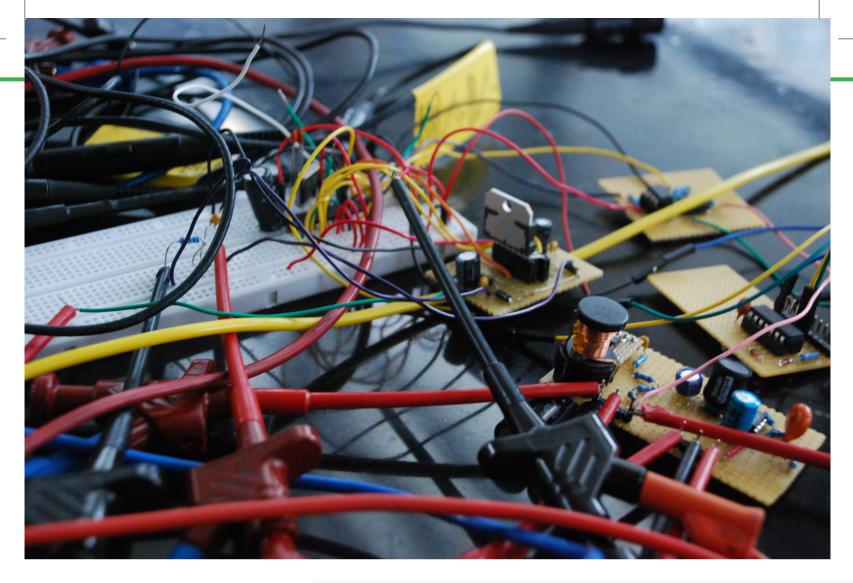

# $(AC/DC)^{-1}$

Solar energy has some advantages over energy from fossil fuels; solar energy does not cause any pollution in the form of carbon dioxide and unlike the supply of fossil fuels, the supply of solar energy will not reduce any time soon. This makes the project for the first year's students at the end of the second quartile very interesting. For the duration of the project they were provided with solar panels. The output of a solar panel is a DC voltage, which had to be fed back into the power grid, through a transformer. The input of the transformer had to be an AC voltage of 12 V effective.

To turn the DC signal into an AC signal, Pulse Width Modulation was used. Because we only used a positive voltage, it was only possible to build a rectified sine wave.

To turn this rectified sine wave into a full sine wave, an H-bridge was used. To make sure the phase of our signal corresponded to the phase of the grid, we used a comparator to check the polarity of the grid. The output of the comparator was sent to the microcontroller, which can adjust the PWM, and "This makes the project very interesting."

therefore the phase of the created sine wave.

The solar panel will deliver the maximum power at a certain ratio between the voltage over the solar panel and the current through Author: Vera Nauta , Pascale van de Ven Photos: Marcel Wenting

the solar panel. To find this maximum power point, the voltage and current are measured and sent to the microcontroller, which will calculate the power. The amplitude of the created sine wave will be varied and the effect on the power will be calculated. This way, the maximum power point can be found. The voltage over the solar panel is not high enough to create the desired amplitude. Therefore, a boost converter was added.

At the end of the project, all systems were tested. Even though our system looked like a total mess, and the maximum power point tracking did not work at all, we were one of the two groups who could actually deliver power to the grid. An overwhelming 1 W to be precise!

"What we really liked about this project was that we were allowed to figure things out ourselves."

What we really liked about this project was that we were allowed to figure things out ourselves. Learning by trying to put theory into practice was a nice addition to the lectures. Some people complained that the project was too hard and that we had no idea what we were doing. The latter is certainly true, but it allowed us to learn a lot of new things. Of course it was also pretty awesome that we were actually able to feed power into the grid. Altogether, we had thee very entertaining weeks!

## Chain Reaction 3D electronics 2B

Each edition of the Vonk has a main article written by one of the research groups at our University. Such an article discusses a recent development or trend in their field of research. It is interesting to listen to an outsider's comment on such a trend, being either positive or negative. For this purpose, starting this Vonk, we intruduce a new feature. As this text will be a critical glance on the previous main article, which in his turn is a comment on a technology or trend, we speak of a Chain Reaction. Anne-Johan Annema sets the ball rolling by commenting on TST's text on self-assembly.

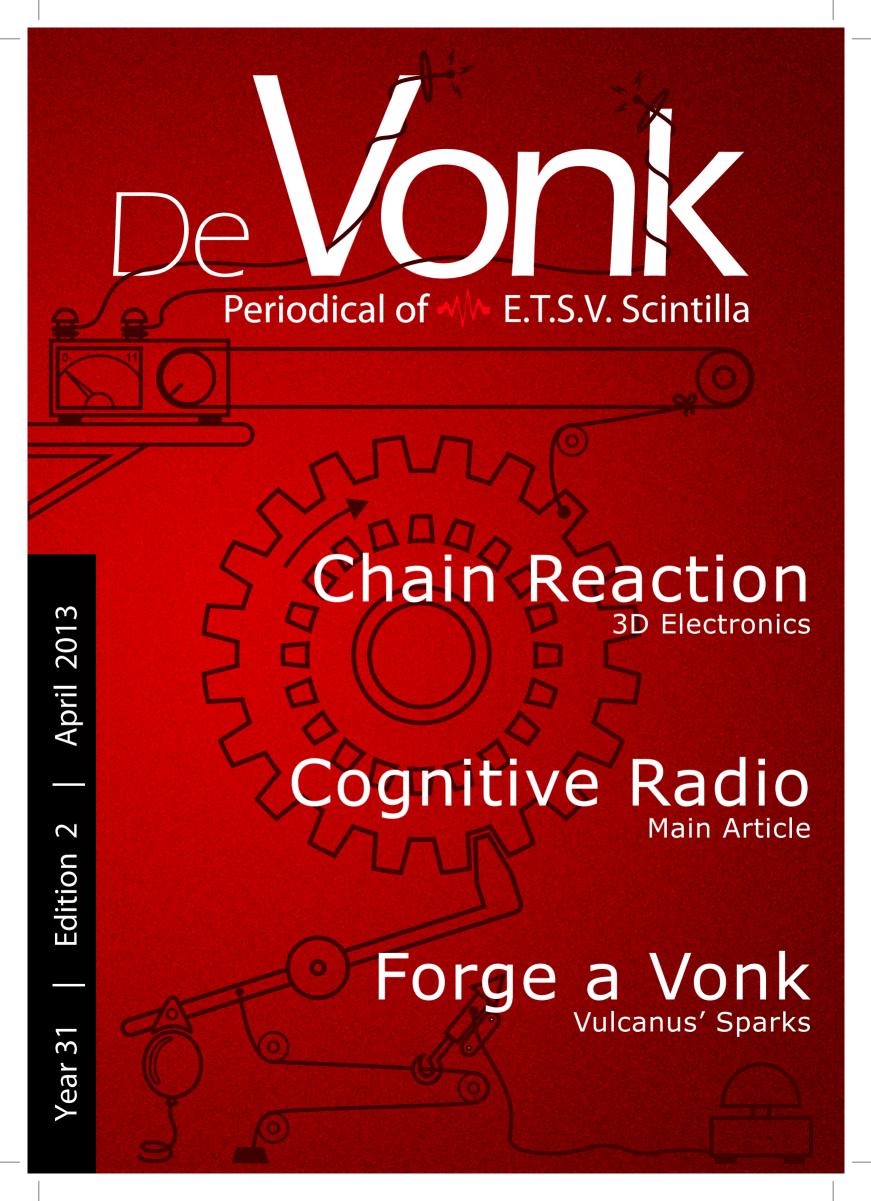

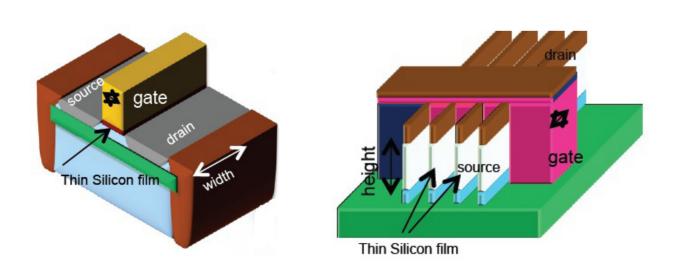

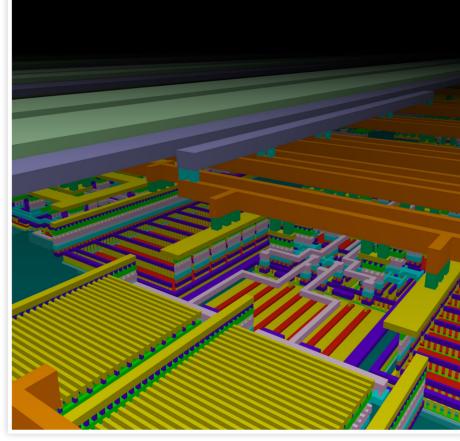

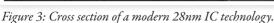

It is frequently assumed that nowadays electronics are made in planar, two dimensional, IC technologies. It is true that CMOS (complementary Metal-Oxide-Semiconductor) transistors that are used in nearly every IC appear to be quite planar. However, already this very basic transistor is a true 3D structure. A cross section of a modern CMOS transistor is shown in figure 1 (from [1]). In the newest technologies that we can access nowadays at ICD the channel lengths are down to 28nm and decreasing to 22nm in about one year. The resolution on 28nm is about 1nm which translates into just a few atoms. The resolution in the vertical direction is even more scary: layers

> "The resolution on 28nm is about 1nm which translates into just a few atoms."

Author: Anne-Johan Annema

that are in the order of 1nm with a very low tolerance (gate oxide layers) and bulk layers with a thickness of about 10nm are available. Adding a relatively thick gate electrode turns this device into a small 3D-structure. Still we regard this MOS transistor as a planar device. Also finfets - which are basically 90 degrees out-of-plane-rotated MOS transistors - can be seen as quasi-planar devices while for marketing reasons they are frequently denoted as 3D-transistors.

Figure 1: Modern MOS transistors [1]: almost planar ultra-thin-body transistors or just-planar-from-a-distance FinFETs

## Nowadays 3D full custom electronics

The true 3D aspect in every modern and in every upcoming CMOS technology is in the interconnects between all transistors and passives in the electronic chip. This interconnection is required to get some nontrivial functionality from an electronic circuit, digital, analog, or mixed-signal.

Usually the interconnect is structured quite hierarchical. At a local (sub-circuit) level transistors and passives are interconnected via horizontal metal lines and vertical metal via's that are specifically designed to make the exact right connections between the various transistors that are usually individually sized, shaped and biased for optimum performance. The interconnect layers for local interconnections are located relatively close to the transistors, and are usually relatively short and narrow. This type of interconnect is equivalent to local roads inside the certain neighborhood in a town. One level up in the hierarchy, the sub blocks with their many local interconnects and components are interconnected to power lines and to signal lines to and from other sub-circuits to form a circuit of subsystems. The interconnects for this purpose are usually thicker metal interconnect layers further away from the actual transistors. Just as any other layer and any component in a high performance electronic chip, this layer is specifically made to get exactly the intended functionality. The interconnects between the sub-circuits are similar to main roads in a town.

In modern systems, this procedure repeats itself one or two times to construct large electronic systems with huge computational power; analog, digital or mixed. The hierarchical approach is essential to handle the overall complexity of the system. At the same time very good interaction and cooperation between designers in all stages is required to get an overall good result. The semiconductor physics guys deliver the components - mainly transistors - that are sized, biased, used, pampered and squeezed out by the circuit designers to push performance. For analog and mixed-signal circuit designers, usually the goal is to approach or even circumvent the physical and practical limits to system performance of each technology. This clearly requires also a lot of knowledge of system level issues, or requires

"For analog, digital and mixed signal electronics, self-assembled electronics are quite hard if not impossible."

a lot of interaction with system level designers.

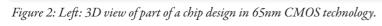

As an illustration for the 3D construction of nowadays electronic chips, figure 2 shows a 3D view of a part of a chip design in 65nm CMOS technology made at the ICD group some years ago [2],[3]. In this view, the transistors are somewhere far down below and are hardly visible. The thin and short local interconnect lines can be seen in the lower layers, while the interconnect lengths and thicknesses increase towards higher layers. In the shown design, 8 metal interconnect layers are used, building a true 3D structure.

Figure 3 shows a cross section of a design in a newer 28nm process [4]. The transistors are located just above the buried oxide (BOX) layer and are not visible on this scale. Mainly visible are the interconnect layers that are thin and narrow at the bottom, for local interconnects, and are wider and more thick towards the top of the 3D structure for long distance signaling and power routing.

## 3D self assembling electronics

For analog, digital and mixed signal electronics, self-assembled electronics are quite hard if not impossible. This is because the electronics are fully customly designed,

both the transistors and the interconnects. Steered assembly just might be done using a Tetris-kind of approach which then would be quite time consuming, assuming that the very small transistors - nowadays down to about 5nm\*30nm\*60nm including drain and source region to contact - can be steered to the exact right position. Also the interconnects must be steered.

But don't get me wrong, the proposal in the previous Vonk is interesting: self-assembly might be used for very regular structures, with very regular active or passive devices and very regular interconnect. The system that satisfies this is a memory. Current advances in memories using transistors include both increasing the lateral packing density and decreasing the physical capacitor size for DRAM. The packing density is effectively tackled by Moore's law, which does not come cheap and which requires many research effort. The physical capacitor size in DRAM can be tackled in electronics and in e.g. making vertical capacitors: digging capacitors into the silicon.

3D self-assembly appears to be a disruptive technology that might push the memory density significantly. Still, the technology must include a non-self-assembled electronics part - fully customly designed - for read and write actions, including proper (regular) interconnects to these electronics. This can be built for example below the memory itself. For a cube memory matrix only custom designed read/write circuits are needed which is quite a bit less than for a conventional square memory matrix, assuming large memories.

#### Future of nowadays 3D full custom electronics

As explained previously, nowadays electronics are and will remain to be designed fully customly, to be able to implement high performance and well defined and non-trivial functionality. To be able to do this, all of nowadays chips are true 3D structures with (quasi) planar active devices (the transistors) and a huge stack of custom designed interconnections to route all supplies and signals. A next step towards even more 3D integration would be stacking a number of today's 3D structures on top of each other using extra vertical (through chip) via's for global power and signal routing. This would be feasible as the lateral dimensions of a chip are in the order of a few mm, while the actual height of the 3D stack is roughly 10um (containing tens of different layers, including the transistors and the many interconnect layers). Stacking tens or more of these structures could become feasible in the future which adds another dimension to our current 3D electronic chips.

Another nice thing about conventional 3D electronics is that the shrinking feature sizes of transistors will stop some day. Upcoming transistors (in a few years) will have gate lengths and interconnect feature sizes of about 10nm which is just about 20 atoms wide. Even then, transistor sizes are expected to continue to shrink for a few years. However, then the major increase in computational power and analog functionality must come from 3D integration of electronic systems, and from smarter circuit designs and smarter system designs. The end of the ever shrinking of transistors just may be the beginning of ever increasing challenges for circuit and system designers.

[1] J. Hartmann, "Planar FD-SOI Technology at 28nm and below for extremely power-efficient SoCs", Symposium: Fully Depleted Transistors Technology - December 10th, 2012 – San Francisco, CA

[2] M.C.M. Soer, screendump of part of his chip design

[3] http://sourceforge.net/projects/gds3d/

[4] L.A. Wolderink, P.J.Kamp and L. Abelmann, "3D self-assembled electronics", Vonk 1, pp 26

# Cognitive radio

Raar idee dat ik vier jaar geleden nog bezig was met afstuderen, en dat nu alweer mijn promotietraject erop zit. Mijn gecombineerde afstudeeropdracht ging over het verbeteren van een geïntegreerde spectrum analyzer, een apparaat waarmee de verschillende frequenties van signalen onderscheiden kunnen worden. Deze afstudeeropdracht voerde ik uit bij de informatica-vakgroep Computer Architectures for Embedded Systems (CAES) van professor Gerard Smit en bij de elektrotechniek-vakgroep Integrated Circuit Design (ICD) van professor Bram Nauta.

Al halverwege mijn afstuderen kwam naar voren dat er een project aan zat te komen waarin de belangrijkste doelstelling was: 'het in kaart brengen en oplossen van problemen om een Cognitive Radio (CR) in goedkope en low-power hardware te realiseren'. Dit onderzoek paste behoorlijk goed bij mijn afstudeeronderwerp en zou bij dezelfde vakgroepen plaatsvinden.

Ik wist niet meteen of ik dit wel wilde; is het niet beter je blik te verruimen, na ruim zeven jaar aan deze universiteit te hebben gestudeerd? Voor alles zijn voor- en nadelen te

"Na vier jaar ben je veel minder ver dan je zou willen"

bedenken, maar tijdens mijn afstuderen was ik er al wel achter gekomen dat onderzoek doen mij wel ligt. De keuze om AIO te worden was dus gemaakt. Gezien mijn brede interesse paste de CR opdracht goed bij mij, omdat het veel vakgebied-overschrijdende onderwerpen kent. Een voordeel was ook dat ik al een soort vliegende start had door mijn afstuderen, wat zeker gunstig is gezien de ervaring van veel AIO's: het eerste jaar ben je vooral aan het inlezen en na vier jaar ben je veel minder ver dan je zou willen. Ondanks de vliegende start ben ik toch minder ver gekomen dan ik van tevoren had gedacht. Dat neemt echter niet weg dat het enorm goed bevallen is, want je hebt een vrijheid die je in het bedrijfsleven niet snel zult tegenkomen. Zowel qua onderwerpen waar je aan werkt als hoeveel tijd je daaraan besteedt, zonder al teveel strikte deadlines.

#### Cognitive Radio

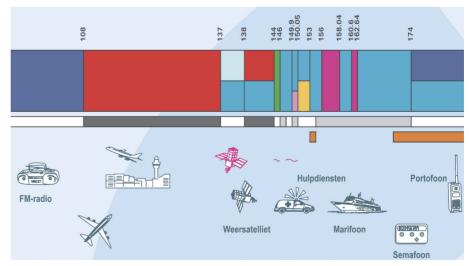

Om te begrijpen wat CR inhoudt, moeten we eerst weten dat draadloze toepassingen op dit moment elk hun eigen stukje spectrum krijgen toegewezen (zie figuur 1), eventueel na betaling, maar zeker pas na

Author: Mark Oude Alink

uitgebreide tests. Ook zijn er enkele zogeheten Industrial Scientific and Medial (ISM)-banden, waar elk protocol na goedkeuring gratis gebruik van mag maken. De meest bekende is de ISM-band op 2.4GHz, waar onder andere WLAN, Bluetooth en ZigBee in opereren. Deze vrij beschikbare bandbreedte is echter zeer beperkt, wat zich praktisch uit in een gelimiteerde snelheid en een gelimiteerd aantal verschillende kanalen in een beperkte ruimte voor WLAN.

Door deze toewijzing is spectrum zo schaars geworden, dat bedrijven grof geld betalen voor een paar MHz bandbreedte. Om een voorbeeld te noemen, in 2008 heeft de

Figuur 1: Versimpelde frequentie-indeling tussen 100MHz en 200MHz in Nederland Bron: Agentschap Telecom

FCC (de toezichthouder op het spectrum in de VS) een veiling gehouden waarin een jaar exclusief gebruik van 52MHz bandbreedte geveild is voor 19.6 miljard dollar. Voor het spectrum in de buurt van de 700MHz werd dus 400 miljoen dollar per MHz neergelegd! Metingen hebben echter uitgewezen dat het gebruik van de statisch toegewezen frequenties sterk varieert. Gemiddeld genomen is het spectrum op een willekeurige plaats en tijdstip slechts voor 3% tot 20% in gebruik. Hier valt dus nog een hoop winst te halen!

De term "Cognitive Radio" is in 1998 bedacht door Joseph Mitola III, die in 2000 op dit onderwerp promoveerde, maar heeft in de loop van de tijd verschillende betekenissen gekregen. IEEE definieert het als volgt: "A type of radio in which communication systems are aware of their environment and internal state and can make decisions about their radio operating behavior based on that information and predefined objectives." Cognitief slaat dus op een mate van intelligentie en adaptiviteit. In de meest ruime zin van het woord bestrijkt CR zich over zeer veel wetenschappelijke gebieden, maar in ons project beperken we 'environment' tot het frequentiespectrum en 'operating behavior' tot het uitzenden en ontvangen op beschikbare frequenties.

#### Enkele onderzoeksrichtingen binnen CR

Zelfs binnen dit beperkte kader, waarin de CR het spectrum scant op zoek naar vrije ruimte om in te zenden/ontvangen, zijn er vele niet-triviale problemen. Ik noem er hier een paar, zonder volledig te willen zijn.

Een vrij zwak TV-signaal, dat nog net sterk genoeg is om ontvangen en gedecodeerd te worden door een TV-ontvanger, komt door een muur (dus nog een keer sterk verzwakt) bij een CR aan. Betekent dit nu dat dit stukje spectrum vrij is of niet? Want hoe weet een CR of er een TV-ontvanger in de buurt is? En hoe weet de CR of het signaal door een muur heen ontvangen wordt of dat het een directe line-of-sight is? Dit is een soort hidden-node problem, maar dan in een nieuwe context.

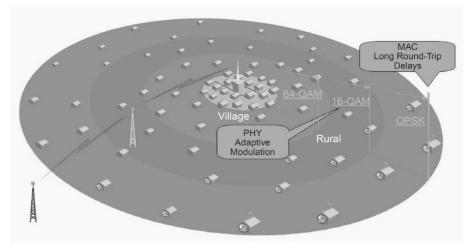

Figuur 2: IEEE 802.22 heeft als doel om landelijke gebieden van breedband-internet te voorzien zonder al te dure infrastructuur door CR-technologie in de TV-banden te gebruiken. Bron: Cognitive radio communications and networks - principles and practice

Hoe wordt de beschikbare bandbreedte verdeeld tussen verschillende CRs? Onderling communiceren, via een master-slave systeem, of gewoon wie het eerste komt het eerste maalt? En hoe beginnen twee CRs überhaupt met communiceren? Het spectrum bij de ene CR kan significant anders zijn dan bij de andere CR. Moet er een gemeenschappelijk control channel zijn? Maar dat betekent weer statische toewijzing. Is dat wel wenselijk, en zo ja, hoe regel je dat op wereldniveau?

Het scannen van het spectrum en het beslissen welke band beschikbaar is, danwel het beste is qua eigenschappen, valt niet binnen één laag van het OSI-layer model. Hoe moet daarmee omgegaan worden? Sommige gelicenseerde gebruikers hebben een (redelijk) vast patroon van frequentiegebruik. Wat voor vorm van kunstmatige intelligentie of patroonherkenning is nodig om dat detecteren, te voorspellen en uit te buiten?

#### Onderzoek naar hardware voor CR

In ons project wordt er vooral gekeken naar het ontwikkelen van hardware om zo'n CR mogelijk te maken; we maken ons niet druk om veel van de eerder genoemde problemen, hoewel ze natuurlijk erg relevant zijn. Het maken van de hardware heeft echter weer zijn eigen problemen, waarvan ik hier de belangrijkste noem.

Bij statische frequentie-toewijzing worden speciale hogekwaliteitsfilters gebruikt om te zorgen dat de zender nauwelijks vermogen buiten zijn frequentiebandje uitzendt, omdat dat anders andere gebruikers zou storen. Deze filters zijn echter duur en totaal niet flexibel. Dit is ook een reden dat bijvoorbeeld een quad-band telefoon een stuk duurder is dan een dual-band telefoon. Hoe moet een flexibele CR dit oplossen? Het is relatief duur en onpraktisch om voor elke mogelijke band een apart filter te hebben. Er zijn wel allerlei digitale filter-technieken mogelijk, maar dat kan veel rekenkracht kosten en daarnaast moet het uiteindelijk alsnog door een niet-ideaal analoog circuit.

Hoe maak je een spectrum analyzer onchip die niet €50.000 euro kost en 200W verbruikt, zoals een moderne spectrum analyzer in het lab, maar die nog wel de benodigde performance levert? Waar kun je op beknibbelen en waar niet? Wat voor processing voer je uit om een beslissing te nemen of een frequentieband vrij is of niet? Hoe zorg je ervoor dat je dat met een energiezuinige processor, die je waarschijnlijk toch al hebt voor andere toepassingen van je (mobiele) apparaat, kunt behappen?

Hoe realiseer je bovenstaande functies in een modern CMOS-proces waarin je slechts ongeveer 1V ter beschikking hebt en waar de transistoren voor digitaal weliswaar erg goed zijn, maar voor analoog niet echt? En hoe zorg je dat de totale powerconsumptie laag genoeg blijft, zodat je niet elke tien minuten je accu hoeft op te laden?

#### Techneuten & Regel- Voordelen van CR gevers

Een erg interessante discussie is die tussen techneuten en regelgevers. De regelgevers willen graag de gelicenseerde gebruikers van het spectrum beschermen, aangezien die vaak grof geld hebben betaald om hun diensten te kunnen aanbieden. Om garanties te kunnen geven dat hun diensten niet gestoord worden, moet een CR zelfs bij hele zwakke signalen deze band al als "in gebruik" markeren.

In verband met allerlei mogelijk effecten die optreden als radiogolven reflecteren en interfereren (bijvoorbeeld fading en shadowing), kan de CR een veel zwakker signaal zien dan een naburige ontvanger van de diensten. Dit betekent dat zwakke signalen gedetecteerd moeten worden, ver onder het ruisniveau van elke ontvangers. Hoe doe je dat als je niet weet wat voor soort signaal het is?

Techneuten vinden daarom veelal dat de limieten omhoog moeten. Televisiezenders zijn daar weer niet blij mee, omdat er dan kans bestaat dat de signaalkwaliteit bij hun abonnees omlaag gaat door de storing veroorzaakt door CRs. Dit soort discussies heeft in 2004 zelfs geleid tot het oprichten van de DySPAN-conferentie, een conferentie waarin regelgevers, onderzoekers en praktiserende bedrijven bij elkaar komen om face-to-face over dit soort zaken te kunnen redetwisten.

Afgezien van efficiënter gebruik van het spectrum, hebben wij als consumenten iets aan CR? Jazeker! Niemand vindt het leuk dat het rond de jaarwisseling niet of nauwelijks lukt om een SMS'je te versturen, hoewel daar natuurlijk nog wel mee valt te leven. Met standaard GSM zijn er simpelweg te weinig kanalen beschikbaar om iedereen te bedienen, terwijl met CR-technologie veel meer kanalen gevonden kunnen worden.

Zeer belangrijk daarentegen is de mogelijkheid om hulpdiensten betrouwbaarder en breedbandiger communicatie te bieden. CR maakt het mogelijk dat de vele medewerkers niet meer gelimiteerd zijn door de 10MHz bandbreedte dat C2000, het huidige systeem, biedt. Dan waren er bij gebeurtenissen, zoals bij de Vuurwerkramp in Enschede in 2000 of de aanslag op Koninginnedag in 2009, geen problemen geweest door overbelasting. Ook staat C2000 bekend om zijn verbindingsproblemen in gebouwen, terwijl een CR de mogelijkheid biedt op een andere frequentie over te schakelen waar wel bereik is. De grotere bandbreedte maakt het ook mogelijk om foto's en/of videobeelden te kunnen overzenden, wat een grote toegevoegde waarde kan hebben.

Een ander voordeel is het mogelijk maken van breedband internettoegang in landelijke gebieden. Voor Nederland is dat niet zozeer een probleem, maar in de VS heeft slechts 51% van de bevolking breedband internettoegang, omdat 75% van de bevolking op 2% van het landoppervlak leeft. Het

is veel te duur om de infrastructuur aan te leggen om iedereen van breedband internet te voorzien. Echter, de frequentieband van 50-860MHz, waar de TV-kanalen zitten, biedt zeer goede propagatie-eigenschappen, waardoor het eenvoudig is om draadloos meer dan 30km te overbruggen. Met CR wordt het dus mogelijk om met weinig investering grote gebieden van breedbandinternet te voorzien, zie figuur 2. Dat is de reden dat zelfs bedrijven als Google en Microsoft op de DySPAN-conferentie aanwezig zijn om hun eigen CR-hardware onder de aandacht te brengen.

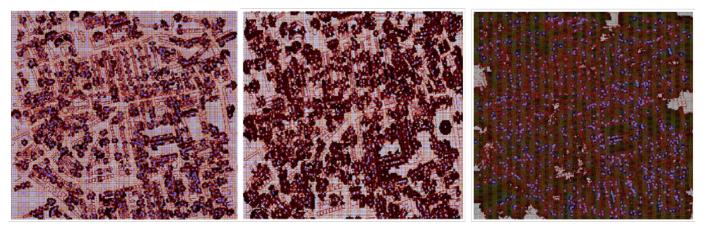

Recentelijk is de IEEE 802.22 standaard in het leven geroepen voor precies deze toepassing, maar dat is niet de enige ontwikkeling. Ook de 802.11 (WiFi) familie krijgt een nieuwe telg, 802.11af, die in de TV-banden opereert. Je zou hiermee bijvoorbeeld simpelweg een snellere WLAN-verbinding in je huis of op de campus kunnen krijgen. British Telecom heeft zelfs al ideeën om met deze technologie de straten van hele wijken in Londen van draadloos internet te voorzien, zie figuur 3.

#### Conclusie

Samenvattend is CR dus een nieuw paradigma voor draadloze communicatie met vele mogelijkheden, waarvoor echter eerst nog vele problemen overwonnen moeten worden alvorens het een succes kan worden. Ons project heeft een aantal van deze problemen verminderd of opgelost. Wellicht dat we deze in een toekomstige Vonk kunnen laten zien.

Figuur 3: WiFi-dekking (simulaties) in Notting Hill, Londen op 5GHz, 2.4GHz en in de TV-band. Bron: British Telecom

## Finger vein recognition Signals and Systems Group

Author: Fieke Hillerström

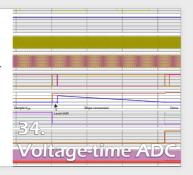

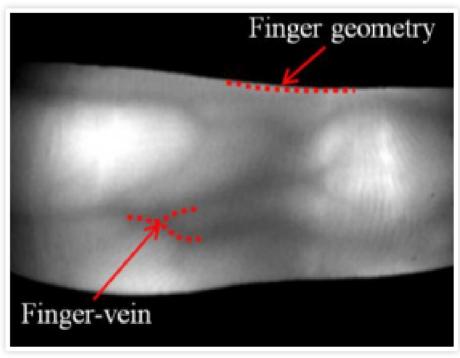

Biometrics are becoming increasingly important for recognition of people. Biometrics refer to the recognition of individuals by their characteristics or traits. Fingerprints and face recognition are traditional methods. Among the recently new recognition methods are the ones focused on finger vein patterns. For the past quartile I have worked on my Bachelor assignment at the Signals and Systems group, focused on finger vein recognition. This assignment proceeds the Master assignment of Bram Ton, who constructed a database of finger vein images. My assignment was to determine the performance of local binary patterns on finger vein recognition. Next to that I looked at the performance of the finger shape as biometric classifier.

Finger vein recognition is a relative new method in the field of biometrics. It uses the crisscrossing vein patterns in a human finger to identify individuals. An example of a finger vein image is shown in figure 1. One of the advantages with respect to the more traditional biometrics technologies is the difficulty of counterfeiting the finger vein patterns. Because the veins are hidden inside the body, the surface conditions of the hands have no influence on the authentication process.

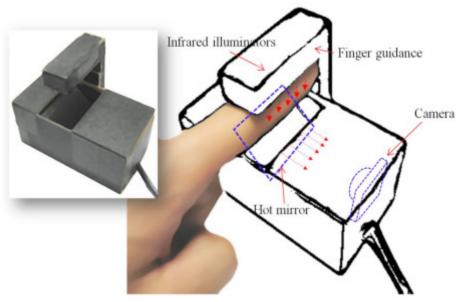

To capture the finger vein images, infrared light is needed, because the patterns are located under the skin. Infrared (IR) light can penetrate relatively deep into the skin and passes through human body tissues, but is absorbed by the hemoglobin in blood. To capture the finger vein images, IR illuminators are placed above the finger such that the light penetrates the finger. An infrared camera is used to capture the images.

Figure 1: Example of a finger vein image

An example of a device to capture them is shown in figure 2.

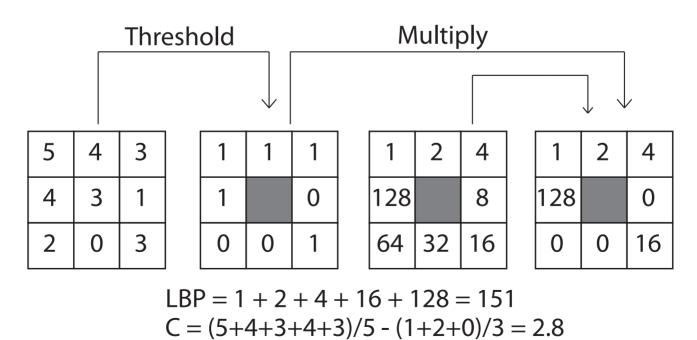

My assignment was to implement local binary patterns (LPBs) on the finger vein images. LPBs are used as a method for texture analysis. Basically it is a binary code describing the local texture pattern, built by thresholding a neighborhood by the gray value of its center. Every pixel in a picture is compared to the values of its neighborhood, which results in a label for this pixel. The outcome of this thresholding results in a binary code, which is converted to a decimal value, as shown in figure 3. The advantage of LPBs are their simplicity and their independency with respect to light exposure.

"Using the finger shape descriptors leads to better performance"

All these LBP values are combined in a histogram, which is used as a texture descriptor. This histogram contains information about the distribution of patterns over the whole image, but loses spatial information. To retain the spatial information, the image could be divided into sub regions

Figure 2: Capturing finger vein images

over which a new histogram is calculated. This histogram is a measure for the amount of different structures in an image. One of the advantages of LBPs is that the method is less dependent on different light exposure in two sample intervals.

Before calculating the LBP histogram for a finger vein image, every image has to be normalized. The finger images need to have the same size and orientation. After this normalization, the local binary pattern histograms are calculated and the edges of the finger image are used as finger shape descriptor. These two classifiers are combined and the performance is determined.

From this research, it can be concluded that using the finger shape descriptors leads to better performance than using the local binary patterns. But the local binary patterns could be promising in combination with more complicated recognition algorithms.

*Figure 3: The process of calculating the local binary pattern of a pixel*

# The Logical Volume Manager

Partitions made easy

Hard disk partitions can be a pain to manage correctly. Sometimes you have a partition that is too small and it needs to be enlarged, or it is too large and you're wasting precious space. Unfortunately partitions aren't flexible and can't easily be resized, even if it is possible it takes hours to do. These problems can be circumvented by using the Logical Volume Manager, if you have Linux.

#### What is the Logical Volume Manager?

The Linux Logical Volume Manager is disk management software. It acts as a sort of vitalisation layer between the partitions and the physical hard disks. The Logical Volume Manager can manage flexible partitions which can be easily configured and changed. The Logical Volume Manager can create, resize and destroy partitions with a few simple commands. For example, one can, when installing the operating system create a few partitions, but only as large as necessary when installing. When it needs more space on this partition, it can extend the partition and continue working. Normally, a partition needs to be one continuous space, but the LVM circumvents this problem. This can all be done on a live system and doesn't require a reboot.

#### How does it work?

The Linux Logical Volume Manager works by utilizing the device mapper kernel module. The device mapper is a generic framework for mapping one block device (for example a hard disk) to another (virtual) block device. It forms the foundation of many hard disk technologies in Linux. The LVM makes use of it, as do software (fake) RAID and encrypted volumes. The device mapper is used to map the virtual partitions

created by the LVM to space on a real hard disk.

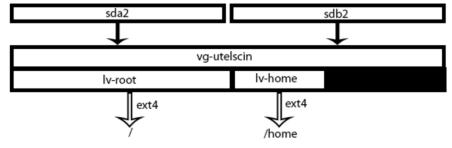

The LVM works as follows. The LVM needs a partition to work with, this is a so called physical volume or PV. This is the space the LVM can use to store data. Physical volumes form the link between the actual hard disk and the Logical Volume Manager. Physical volumes are grouped together in a

volume group or VG. The volume group is the main working unit of the LVM. It manages the physical volumes it consist of and with that the total space of the hard disk pool.

From the volume group we can create logical volumes (LV), which can be used as partitions for a system. The logical volumes can be accessed as real disks. A logical volume can be formatted to have a file system on it and is the resulting storage block of the Logical Volume Manager.

Each physical volume in a volume group has some space reserved to store the entire layout of the volume group. Thus if a physical volume goes missing, for example it breaks down, the entire layout of the volume group

#### oot@utelscin:~\$ fdisk -1

| Disk /dev/sda: 2 | 50.1 GB. 25 | 0059350016 1 | vtes         |       |               |

|------------------|-------------|--------------|--------------|-------|---------------|

| 255 heads, 63 se |             |              |              | . 488 | 397168 sector |

| Units = sectors  |             |              |              |       |               |

| Sector size (log | ical/physic | al): 512 byt | es / 512 byt | es    |               |

| I/O size (minimu |             |              |              |       |               |

| Disk identifier: |             |              |              |       |               |

|                  |             |              |              |       |               |

| Device Boot      | Start       | End          | Blocks       | Id    | System        |

| /dev/sda1 *      | 2048        | 194559       | 96256        | 83    | Linux         |

| /dev/sda2        | 194560      | 488396799    | 244101120    | 8e    | Linux LVM     |

|                  |             |              |              |       |               |

| Disk /dev/sdb: 2 | 50.1 GB, 25 | 0059350016 H | ytes         |       |               |

| 255 heads, 63 se | ctors/track | , 30401 cyli | nders, total | . 488 | 397168 sector |

| Units = sectors  | of 1 * 512  | = 512 bytes  |              |       |               |

| Sector size (log | ical/physic | al): 512 byt | es / 512 byt | es    |               |

| I/O size (minimu | m/optimal): | 512 bytes /  | 512 bytes    |       |               |

| Disk identifier: | 0x00096769  | )            |              |       |               |

|                  |             |              |              |       |               |

| Device Boot      | Start       | End          | Blocks       | Id    | System        |

| /dev/sdb1        | 2048        | 194559       | 96256        | 83    | Linux         |

| /dev/adh2        | 194560      | 488396799    | 244101120    | 80    | Linux LVM     |

#### Figure 2

can still be recovered. The rest of the physical volume is divided into small parts between 8 KB and 512 MB called Physical Extends (PE). These form the basic building blocks of a logical volume and are used to store your data.

A Logical volume exists of Logical Extends (LE). These map directly to one or more physical extend on the physical volume. This mapping between logical extends and physical extends is what the Logical Volume Manager gives its flexibility. A Logical volume can appear as one continuous space to the operating system, but can in fact be spread across multiple disks. The data is no longer bound to a specific area of the hard disk.

With this mapping, we can build a logical volume from a volume group. We can map a number of logical extends to a number of physical extends and create a partition of a certain size. The physical extends don't have to be contiguous and can be from any disk of the volume group. This feature indirectly enables us to make partitions larger than a single disk of a volume group. If we need a larger volume, we can instruct the LVM to add more extends to a logical volume. If it can do with less space we could instruct the LVM to remove some empty extends from the volume and shrink it.

With these tools we can resize any volume to fit our size requirements. Afterwards we only have to notify the file system on it that the volume under it has changed. A few file systems support live resizing and can adapt to the changes of the underlying volume. There are no limitations in the number of logical extends a logical volume can have. When given enough disks, a volume group could grow indefinitely. There's no IO penalty on using larger or smaller extends,

"When given enough disks, a volume group could grow indefinitely."

only the tools for managing the logical volumes could suffer from a penalty. We could use larger extends, but a logical volume can only grow in steps of the size of an extend. So if we pick 512 MB as an extend size we can only grow our volume in steps of 512 MB. For most systems the default size of 4 MB is suitable.

#### Basic usage

If we want to use the Logical volume manager we first need a partition we can use as physical volumes. In the case of Utelscin, one of Scintilla's servers, we have two disks with each a separate partition for our physical volume (figure 2). We have sda2 and sdb2 as our physical volumes. Before we can use these as a physical volume we have to format them as physical volumes. This can be done with "pvcreate". For example: "pvcreate /dev/sda2" creates a physical volume on the partition sda2. As visible in figure 2, the partition also gets Linux LVM as a label so it can be identified as a physical volume. We can ask our systems which physical volumes it had with "pvdisplay". An example of this is given in figure 3. As we can see we have 2 physical volumes and we can view some statistics about these volumes.

Now that we have our physical volumes, we can create a volume group with our physical volumes. With "vgcreate vg-utelscin / dev/sda2 /dev/sdb2" we create the volume group named "vg-utelscin" consisting of the physical volumes sda2 and sdb2. The name of the volume group is used as an identifier for the group and is used in most commands to specify which group the command applies to. Therefore it makes sense to use either a prefix or a suffix to identify it as a volume group, in this case the "vg-". Also here we have a command to display statistics, not surprisingly called vgdisplay. The result of this for Utelscin can be seen in figure 4. We can see that the volume group has 2 active physical volumes and that there's about 150 GB of free space remaining. This is space that is not yet allocated to a logical volume. Do not confuse this with free space on partitions.

From our new volume group we can create logical volumes. The creation of the volumes is the most complicated command of the LVM. This is because there are many options to select from for more advanced configurations. If we want to create a simple volume for our root partition we can use the following command: "lvcreate -L5G -nlvroot vg-utelscin". This creates a new logical volume of 5GB named ly-root in the volume group vg-utelscin. As with the volume groups, we used a prefix to identify the logical volume as one. There's now a partition that can be used for the system. However, before it can be used it needs a file system. Thus it needs to be formatted with a file system, for example ext4 with "mkfs.ext4".

If our 5 GB is not enough we can extend the volume with another 5 GB to make it 10 GB in size with "lvextend -L+5G /dev/

| root@utelscin:~\$ pv | display                                |

|----------------------|----------------------------------------|

| Physical volu        | me                                     |

| PV Name              | /dev/sda2                              |

| VG Name              | vg-utelscin                            |

| PV Size              | 232.79 GiB / not usable 4.00 MiB       |

| Allocatable          | уез                                    |

| PE Size              | 4.00 MiB                               |

| Total PE             | 59594                                  |

| Free PE              | 19081                                  |

| Allocated PE         | 40513                                  |

| PV UUID              | jA6DnK-rXK6-V8Dp-qScH-PBZi-2uv3-MLRyez |

|                      |                                        |

| Physical volu        | me                                     |

| PV Name              | /dev/sdb2                              |

| VG Name              | vg-utelscin                            |

| PV Size              | 232.79 GiB / not usable 4.00 MiB       |

| Allocatable          | уез                                    |

| PE Size              | 4.00 MiB                               |

| Total PE             | 59594                                  |

| Free PE              | 19087                                  |

| Allocated PE         | 40507                                  |

| PV UUID              | VN99og-v5pn-fJXw-uI5N-cKZ2-5IO2-KXgjVf |

Figure 3

vg-utelscin/lv-root". ext4 supports live resizing with resize2fs so we don't have to take down this partition to resize it. Of course as with physical volumes and logical volumes we can view statistics about our new logical volume with lvdisplay. In figure 5 we can see the result of "lvdisplay /dev/vg-utelscin/lv-root". On Utelscin this volume is currently 22 GB and is mapped

#### "Many configurations are possible."

to 2 physical volumes. There are many more commands for managing your volumes. All of these starting with pv for operations on physical volumes and vg and lv for volume groups and logical volumes.

#### More possibilities

With the possibilities of the device mapper, we can do much more than just map one logical extend to a random physical extend. Many configurations are possible. Since the LVM can use any block device for its partitions it is possible to stack multiple layers on top of each other. A lot of setups use a RAID configuration with on top of that a physical volume for added flexibility. Other possibilities include using a encryption layer with a physical volume for flexibi-

lity and creating multiple partitions on top of the encryption layer.

But the LVM can do some nice tricks on its own too. Most of these trick use a creative mapping of the logical extends to the physical extends.

Lets assume we have a disk which is starting to fail. Obviously we want to swap it for a new healthy drive but we don't want any downtime or nasty partition copying. We can add the new disk live to our server. We can then create a new physical volume on this disk and let the LVM move all the physical extends of the old drive to our new drive. The LVM will first copy a physical extend to the new drive. Then it changes the mapping of the logical extend to the physical extend. This way the operating system doesn't notice any downtime or any changes to the logical volume.

Another option is that we can map the logical extends of a logical volume each to two physical extends on different physical volumes. This creates a logical volume that is mapped to two physical volumes. This way, the data is stored on two physical disks, this way if one of the disks fails we still have our data on the physical extends of the other disk. Readers with a bit of knowledge in this field will recognise this as a RAID1 setup or mirroring. The LVM is able to do a number of operations on these volumes. We can while staying live split of a mirror and create a new logical volume with it. We can even split it off, track everything that changes while being split of. Later we can merge the separate volumes together and synchronise everything that has changed in the meantime. This can be used to split off a complete partition, hand the hard disk to someone. He then can change a few files or add something and merge it back into your disk array, letting the Logical Volume Manager handle the syncing between the disks. An other option is to alternatively map logical extends between disks, mapping logical extend 1 to physical extend 1 on physical volume 1, mapping LE2 to PE1 on PV2

| root@utelscin:~\$ vgdisp | lou                                    |

|--------------------------|----------------------------------------|

| Volume group             | IAY                                    |

|                          | vq-utelscin                            |

| System ID                | vg acciscin                            |

| Format                   | lvm2                                   |

| Metadata Areas           |                                        |

| Metadata Sequence No     |                                        |

|                          | read/write                             |

|                          |                                        |

| VG Status                | resizable                              |

| MAX LV                   | 0                                      |

| Cur LV                   | 24                                     |

| Open LV                  | 22                                     |

| Max PV                   | 0                                      |

| Cur PV                   | 2                                      |

| Act PV                   | 2                                      |

| VG Size                  | 465.58 GiB                             |

| PE Size                  | 4.00 MiB                               |

| Total PE                 | 119188                                 |

| Alloc PE / Size          | 81020 / 316.48 GiB                     |

| Free PE / Size           | 38168 / 149.09 GiB                     |

| VG UUID                  | 1XVrJ7-29fi-rNC2-JSnj-F0bf-soxh-a7fM0z |

Figure 4

| root@utelscin:~\$ lvdispla           | ay /dev/vg-utelscin/lv-root            |

|--------------------------------------|----------------------------------------|

| Logical volume                       |                                        |

| LV Path                              | /dev/vg-utelscin/lv-root               |

| LV Name                              | lv-root                                |

| VG Name                              | vg-utelscin                            |

| LV UUID                              | O9CisX-eUxM-pXB1-KoXm-xOP8-acmR-n1eXCb |

| LV Write Access                      | read/write                             |

| LV Creation host, time               | ,                                      |

| LV Status                            | available                              |

| # open                               | 1                                      |

| LV Size                              | 22.00 GiB                              |

| Current LE                           | 5632                                   |

| Mirrored volumes                     | 2                                      |

| Segments                             | 1                                      |

| Allocation                           | inherit                                |

| Read ahead sectors                   | auto                                   |

| <ul> <li>currently set to</li> </ul> | 256                                    |

| Block device                         | 253:4                                  |

Figure 5